‘시스템 반도체’ 회로 설계 정확성 개선

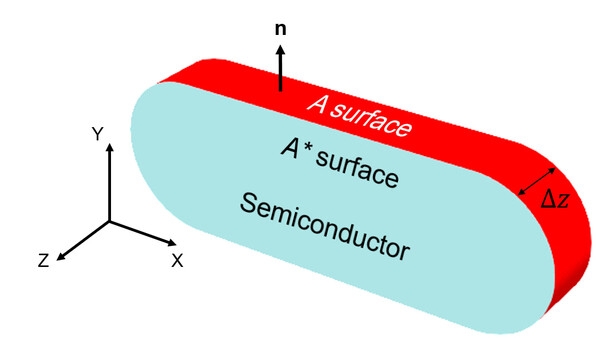

▲ 트랜지스터 단면모습. 지스트 제공

이번 연구 성과로 콤팩트모델의 한계에 따른 오차를 줄여 시스템 반도체 설계의 정확성을 개선할 수 있을 것으로 기대된다.

지스트 연구팀은 트랜지스터의 단면 모양이 다르더라도 게이트 전압에 따른 전하량은 경험적 관계식을 근사적으로 따른다는 사실에 착안해 어떤 트랜지스터 단면에도 적용할 수 있는 보편적인 관계식을 유도해 계산 결과의 최대 오차를 6% 이하로 낮추는데 성공했다.

홍성민 지스트 교수는 “이번 연구 성과는 콤팩트모델의 유도 과정을 명확하게 밝히고 정확도를 향상시켰다는 데 가장 큰 의의가 있다”라며 “향후 반도체 소자 시뮬레이션과 콤팩트모델을 하나로 연결하기 위한 연구에도 기여할 것으로 기대된다“라고 말했다.

한편 시스템 반도체는 연산?제어 등의 정보처리 기능을 가진 반도체이다. 삼성전자는 2030년까지 시스템 반도체 분야 연구개발 및 생산시설 확충에133조 원을 투자하고, 전문 인력1만 5000명을 채용한다고 2019년 발표했다.

글로벌 반도체 품귀 현상에 따라 반도체 주문에서 최종 납품까지 걸리는 시간이 계속 늘고 있는 가운데, 특히 시스템 반도체 분야에서는 설계의 정확성을 위해 정확한 트랜지스터콤팩트모델이 필수적이다.

Copyright ⓒ 서울신문 All rights reserved. 무단 전재-재배포, AI 학습 및 활용 금지

![THE NEXT : AI 운명 알고리즘 지금, 당신의 운명을 확인하세요 [운세 확인하기]](https://img.seoul.co.kr/img/n24/banner/ban_ai_fortune.png)